wlcsp series

分类: wlp serieswlp technology

technology overview

wafer level package is defined as all the assembly and test process are in wafer, and all of input/output (i/o) distribute within the chip surface, which is a kind of i/o fan-in wafer level package, its core characteristics is to use redistribution layer technology to reconfigure the pad in the perimeter of the chip, and then finish the bumping formation (or solder ball). the chip area size of the structure and the final package area size are 1:1 of the standard. the single package formed after packaging can be directly applied to the assembly process.

wafer level package has more process optimization than traditional packaging process, and has great consistent with the chip size, containing redistribution layer (rdl), wafer bumping, wafer level testing (cp or wafer sort), wafer singulation and packing with carrier tape, which is able to support one-stop turnkey outsourcing service of advanced packaging solutions.

applications

wafer level package is one of hotspots in the field of the current packaging and the integration of technology, including ic design, wafer fabrication, assembly and test, substrate manufacturing. wafer level package has two main fields of application, first one is bumping, for high pin count and/or high performance asics, cpu/gpu, gaming, smart ap processor,memory, rf, etc; the second one is smallest chip size package (csp) and the advantage of better electrical performance, and is chiefly used at low pin count package of consumer portable products (including analog/mixed signal, wireless, pmic, automotive electronics, etc.), also can meet memory chips packaging characteristics with lightweight and ultra-thin/large-sized requirements.

features

die sizes

◆ minimum 0.4mm x 0.2mm

◆ advance nodes to 5 nm/4 nm

repassivation types

◆ pi

◆ pbo

◆ lcp

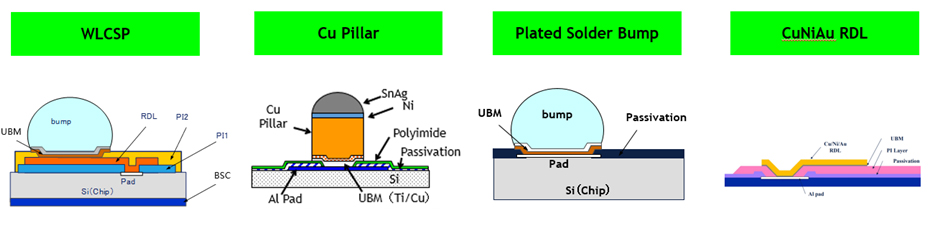

metal types

◆ sputtering ti/cu

◆ sputtering bsm al/ti/niv/au

◆ plating cu rdl/cu ubm

◆ plating cuniau rdl

bump types

◆ lead-free bumping

◆ sac105/266/305/405

◆ cu pillar (cu/ni/snag, cu/sn, cu/snag)

◆ array and fine pitch peripheral, pillar pitch down to 80um, solder bump pitch down to 130um

bsc types

◆ 25um/40um thickness

◆ mainly used lamination

◆ normal bsc or through ir bsc, and 2in1 tape

wlp test

wlp test provides customers with a full range of test platforms and engineering services to support a wide range of analog and mixed signal, automotive, radio frequency (rf), high-performance caculated devices, baseband memory devices, lcd driver devices, power module devices and specific application integrated circuits, such as cpu, gpu, and high performance networking products.

our full turnkey solutions designed to be faster time to market, which include wafer bump services, wafer sort services, final test and post-test services delivering ,the lowest cost of test to our customers and the fastest time-to-market.

tfme advanced probe services supports known good die (kgd) binning, thin wafers, high volume devices with both soft dock and direct docking for sensitive devices, and also contains probe card maintenance capability.

services include

wafer size :

◆ 6", 8 " & 12"

◆ 8 “ frame wafer ,12 “ taiko wafer

wafer testing type :

◆ pad wafer

◆ bump wafer (solder/cu pillar/gold bump)

◆ wlcsp

temperature :

◆ room temp, high temp ,cold temp(temp range:-50-150℃)

docking method :

◆ cable mount & hinge-docking

◆ pogo tower docking

◆ direct docking

通富微电子股份有限公司

地址:中国江苏省南通市崇川路288号

邮编:226004

email: