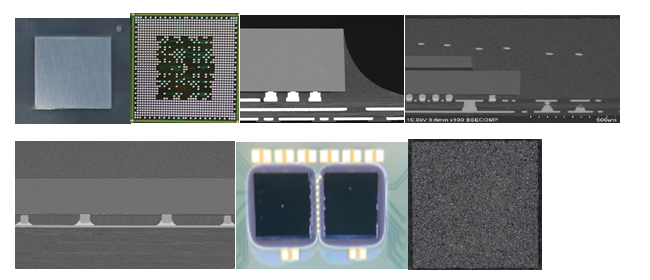

fccsp series

分类: fccsp seriesfccsp technology

technology overview

flip chip interconnection, also knownas controlled collapse chip connection, c4, chip connection, c2, has been identified as a high performance packaging solution to meet the growing need for products with increased electrical performance, high i/o, and high system reliability as a replacement for conventional wire bond packaging technology. utilizing whole die area for electrical connection, substrate i/o per unit increases exponentially compared to perimeter wire interconnection technology.

flip chip interconnect also allows direct connection with on-die power planes which enables increased electrical performance including increased switching speed and more efficient power distribution to the ic performance at lower operating voltages.

applications

flip chippackage technology is considered one of the most established technologyfor high pin count and/or high performance. fc csp provide package solution for smartphones, networking/connectivitydevices.

features

die sizes

◆ 0.35mmx0.35mm~12mmx12mm

◆ advance nodes to 5 nm

substrates:

◆ 2-6 layer laminate build-up substrates

◆ ets,mis,msap

◆ surface finish with osp, niau, enepig,sop

◆ standard strip sizes: 240mmx76.3mm and 240.5mmx95mm

bump types

◆ cu pillar(cunisnag)

◆ solder bump (snag)

◆ pitch down to 79um for cu pillar

◆ pitch down to 130um for solder bump

package technologies

◆ bare die (with or wo lid)

◆ exposed die

◆ cuf(capillaryunderfill)

◆ muf(moldedunderfill)

◆ down to 0.35 mm bga ball pitch

◆ passive component size down to 008004

flip chip csp test

◆ provides a competitive test solution to our customers ranging from test development, platform conversion, and product maintenance and test data analysis.

◆ hasextensive test development experience of various product portfolio, including high-end digital, mix-signal, soc and high-speed products.

◆ reduce customer overhead by outsourcing projects / tasks to avoid maintaining a large scale of dedicated team

◆ incorporate industrial standard through leveraging best known method from our database & continuous cost saving by driving test time reduction, yield improvement

services include

◆ wafer sort test development

◆ final test development

◆ low cost platform conversion

◆ multi-site enablement

通富微电子股份有限公司

地址:中国江苏省南通市崇川路288号

邮编:226004

email: